# SecSi Product Development: Techniques for ensuring Secure Silicon applied to open-source Verilog projects Joe FitzPatrick (SecuringHardware.com) joefitz@securinghardware.com

#### Note

This document is a preliminary revision. For the latest version, please see <u>http://securinghardware.com/secure-opencores</u>

#### Abstract

Secure development processes for software have formed, developed, and matured in the past decade to the point where there are well defined categories of security bugs and proven methods to find them. Secure hardware development, on the other hand, is essentially undefined at this point. Most developers of integrated circuits do no hardware security validation, or are secretive about their methods and findings.

Three separate Open-Source CPU designs were chosen and their verilog source code was reviewed for common security vulnerabilities. This paper will first introduce each of these designs and then identify security vulnerabilities discovered. This paper will discuss the process that that lead to discovery, potential means for exploiting the flaw, and finally methods of fixing it. This paper will conclude by generalizing these bugs into a checklist of common hardware vulnerabilities

### Introduction

Software stacks continue to grow, enabling new and different ways of accessing and utilizing the increasing computing capacity available today. New software layers are gradually being designed with a pro-active approach to security while the supporting layers continue to be refined and secured.

All of this software depends on a solid hardware foundation. From purely a reliability perspective, hardware does exactly that and continues to improve. However, due to a number of factors, integrated circuit devices do not get nearly the same scrutiny in terms of security. Attacking hardware is inherently slower, more difficult, and more expensive that software. In most cases the attacker must be physically present with the need to carefully observe and manipulate electronics, always with the risk of permanently destroying the target device. This plays a strong part of the 'it's in hardware so we can trust it' mindset that even paranoid software security professionals get caught in.

### Background

There is no doubt that many people are doing security validation of hardware designs; however, outside of academia, there is not much public dialog about methods and practices. Newcomers to the field have no reference manuals or seminal works, and no idea of where to start. Established hardware security validation teams are not benefiting from any techniques that are not home grown.

Likewise, while formal verification and other methods promise future solutions to hardware security, the current state of the industry reflects the state of software security 15 years ago where a few minutes of manual inspection can reveal multiple bugs on what is considered a mature and stable system.

In the interest of starting a conversation about hardware security validation methods, This paper will document some of them as applied to actual real-world, publicly-available Verilog code. Three different stable 'Opencores Certified' projects from opencores.org were used as examples in lieu of contrived code blocks or heavily redacted snippets of proprietary code.

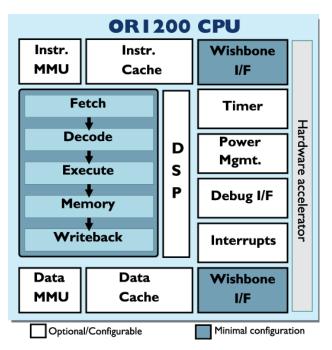

## OpenRisc

OpenRISC is a completely open-sourced RISC CPU architecture developed by the OpenCores Community. The current implementation is the OpenRISC 1200 written in Verilog. It is considered stable, has mainline Linux kernel support, is used heavily by academia, and has also been implemented in a number of commercial products.

#### http://www.rte.se/blog/blogg-modesty-corex/openrisc-1200-soft-processor

Openrisc is combined with several other open components into OpenRISC Reference Platform System-on-Chip or ORPSoC. We conducted a security-minded code review of the latest ORPSoCv2 Verilog source available from Opencores.org. Since this review was of generic Verilog code and not tied to a specific implementation, it's difficult to determine 'exploitability' of any noted issues. Despite that, the issues identified are either likely to be exploitable, or representative of issues that could be exploitable.

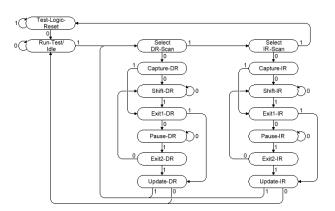

#### One-Hot and JTAG

A common construct in hardware designs is a State Machine. The contents of a register define how the machine behaves, and the machine's behaviour combined with the current state will determine the next state to be loaded.

One-hot encoding is often used for storing the current state of a machine. This means there is a single bit for each state, and only one bit is set at a given time. While this requires extra bits of storage, it eliminates the need for any decoding logic and makes it easier to detect invalid states.

ORPSoCv2 implements JTAG as a one-hot state machine. It defines a single register for each jtag state:

| // Reg | isters                             |  |

|--------|------------------------------------|--|

| reg    | <pre>test_logic_reset;</pre>       |  |

| reg    | <pre>run_test_idle;</pre>          |  |

| reg    | <pre>select_dr_scan;</pre>         |  |

| reg    | capture_dr;                        |  |

| reg    | shift_dr;                          |  |

| reg    | exit1_dr;                          |  |

| reg    | pause_dr;                          |  |

| reg    | exit2_dr;                          |  |

| reg    | update_dr;                         |  |

| reg    | <pre>select_ir_scan;</pre>         |  |

| reg    | capture_ir;                        |  |

| reg    | <pre>shift_ir, shift_ir_neg;</pre> |  |

| reg    | exit1_ir;                          |  |

| reg    | <pre>pause_ir;</pre>               |  |

| reg    | exit2_ir;                          |  |

| reg    | update_ir;                         |  |

The implementation of this one-hot state machine is clearly derived directly from the JTAG spec and is in fact functionally compliant. Each state has an always @ block which is triggered on tap reset or tclk, and each of the 16 blocks are structured similarly:

```

// test logic reset state

always @ (posedge tck pad i or posedge

trst pad i)

begin

if(trst pad i)

test_logic_reset<= 1'b1;</pre>

else if (tms reset)

test_logic_reset<= 1'b1;</pre>

else

begin

if(tms pad i & (test logic reset |

select_ir_scan))

test_logic_reset<= 1'b1;</pre>

else

test logic reset<= 1'b0;</pre>

end

end

// run_test_idle state

always @ (posedge tck_pad_i or posedge

trst pad i)

begin

if(trst_pad_i)

run test idle<= 1'b0;</pre>

else if (tms_reset)

run test idle<= 1'b0;</pre>

else

if(~tms pad i & (test logic reset |

run test idle | update dr | update ir))

run test idle<= 1'b1;</pre>

else

```

|     | run | test | _idle<= | 1'b0; |  |  |

|-----|-----|------|---------|-------|--|--|

| end |     |      |         |       |  |  |

The first assignment sets the state in the event TRST is asserted. The second sets the state if tap reset is triggered via TMS. The third and fourth assignments set the state based on the combination of previous state and the value of TMS.

Functionally, this is correct. Assuming only one JTAG state is asserted, only one next state will be valid. Just like with software, exploitation usually comes down to undermining assumptions. If we can find a way to set multiple state registers to '1' at the same time, we will begin operating this state machine with two active states since there is currently no logic to differentiate between one-hotness or one hot mess.

There is no obvious logical path to set an extra bit in the state. While a few of the state registers are visible as outputs, none are settable as inputs:

| // TAP | states                                |

|--------|---------------------------------------|

| output | <pre>shift_dr_o;</pre>                |

| output | pause_dr_o;                           |

|        | update_dr_o;                          |

| output | capture_dr_o;                         |

|        |                                       |

| assign | shift_dr_o = shift_dr;                |

| assign | pause_dr_o = pause_dr;                |

|        | update_dr_o = update_dr;              |

| assign | <pre>capture_dr_o = capture_dr;</pre> |

|        |                                       |

Due to the very similar parallel structure of the state generating blocks, a timing attack is not initially obvious, however there is one outlier:

```

if(~tms_pad_i & (test_logic_reset |

run_test_idle | update_dr | update_ir))

run_test_idle<= 1'b1;</pre>

```

There are 4 different paths to the run-test-idle state, making this assignment dependent on the combination of 5 separate inputs. Although this depends heavily on syntesis optimization and FPGA architecture, If the FPGA's LUT are only 4-input, it means that run-test-idle's assignment will be the only one with cascading layers of logic. Combined with the fact that TCK is typically an externallycontrolled pin, It is conceivable to 'spawn' an extra state bit into run-test-idle by manipulating TMS.

The next step is to determine what exactly to do with this 'ghost' state. This particular flaw is difficult to exploit because of the iterative paths in jtag:

The most obvious way to interfere with JTAG would bet to traverse both the IR and DR paths at the same time. By spawning an extra state during Select-DR-Scan, Exit2-DR, or Exit2-IR, Two adjacent states could exist that would eventually traverse down IR and DR paths simultaneously. The impact would be that TDI data would shift into both the IR and DR at the same time. Examining the code indicates that IR takes precedence over DR on TDO.

| 1                                                    |  |  |  |

|------------------------------------------------------|--|--|--|

| **********                                           |  |  |  |

| *****                                                |  |  |  |

| *                                                    |  |  |  |

| *                                                    |  |  |  |

| * Multiplexing TDO data                              |  |  |  |

| *                                                    |  |  |  |

| *                                                    |  |  |  |

| *                                                    |  |  |  |

| *******                                              |  |  |  |

| ***********                                          |  |  |  |

| <pre>always @ (shift_ir_neg or exit1_ir or</pre>     |  |  |  |

| <pre>instruction_tdo or latched_jtag_ir_neg or</pre> |  |  |  |

| idcode_tdo or                                        |  |  |  |

|                                                      |  |  |  |

| mbist_tdi_i <b>or</b>                                |  |  |  |

| bypassed_tdo)                                        |  |  |  |

| begin                                                |  |  |  |

| <pre>if(shift_ir_neg)</pre>                          |  |  |  |

| <pre>tdo_pad_o = instruction_tdo;</pre>              |  |  |  |

| else                                                 |  |  |  |

|                                                      |  |  |  |

In the end, there's no clear juicy exploit hiding here yet. JTAG tends to interconnect to nearly everything in a SOC somehow or another:

- What if DR had precedence over IR on TDO?

- What other functions of the chip respond to the current JTAG state?

- Oftentimes, chips enter interesting operating states between Capture-xR and Update-xR states.

- What if these operating states collide?

Beyond JTAG-specific considerations, these observations should apply to all one-hot encodings. If there is enough reason to implement a state as one-hot, there should be enough reason to validate that the state is in fact one-hot, and have a defined failure-recovery reset state. It is important to remember, however, that assertions are not helpful in this regard since they are not synthesized.

As an added bonus, here's an extra JTAG bug:

| /                                           |  |  |  |

|---------------------------------------------|--|--|--|

| ***************************************     |  |  |  |

| ********                                    |  |  |  |

| *                                           |  |  |  |

| *                                           |  |  |  |

| * idcode logic                              |  |  |  |

| *                                           |  |  |  |

| *                                           |  |  |  |

| *                                           |  |  |  |

| *****************                           |  |  |  |

| *************************************/      |  |  |  |

| <pre>reg [31:0] idcode_reg;</pre>           |  |  |  |

| <pre>reg idcode_tdo;</pre>                  |  |  |  |

|                                             |  |  |  |

| <pre>always @ (posedge tck_pad_i)</pre>     |  |  |  |

| begin                                       |  |  |  |

| <pre>if(idcode_select &amp; shift_dr)</pre> |  |  |  |

| idcode_reg <= {tdi_pad_i,                   |  |  |  |

| <pre>idcode_reg[31:1];</pre>                |  |  |  |

| else                                        |  |  |  |

| <pre>idcode_reg &lt;= `IDCODE_VALUE;</pre>  |  |  |  |

| end                                         |  |  |  |

|                                             |  |  |  |

| <pre>always @ (negedge tck_pad_i)</pre>     |  |  |  |

| begin                                       |  |  |  |

| idcode_tdo <= idcode_reg[0]; // JB 100911   |  |  |  |

| end                                         |  |  |  |

|                                             |  |  |  |

It appears to be fine. If we're in shift\_dr, and idcode is the selected IR, shift TDI through the idcode register. Otherwise, reset it. However, this breaks the Pause-DR state's functionality, which is supposed to be sort of an idle state that preserves the contents of DR, while this implementation would obliterate it.

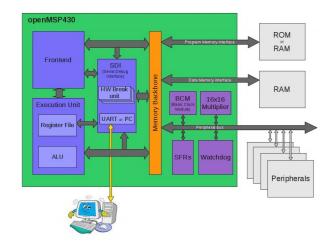

#### OpenMSP430

openMSP430 is a open-source implementation of TI's 16-bit MSP430 architecture, capable of accurately executing code from any MSP430 toolchain. This represents a much smaller scale processor with a simpler microarchitecture than OpenRISC:

OpenMSP430 may be simpler than OpenRISC, but it still has separate frontend and execution stages. Again, we examined the Verilog code in the Opencores.org SVN repository, looking for potentially exploitable security bugs.

#### Frontend State Machine Clocking

On first appearance it is clear that openMSP430 has a very different coding style. The state machine for the frontend is contained in a single always@ block as shown:

```

// States Transitions

always @(i state

or inst sz or inst sz nxt

or pc_sw_wr or exec_done or

irq detect or cpuoff

or

cpu_halt_cmd or e_state)

case(i_state)

I IDLE

: i_state_nxt = (irq_detect &

~cpu_halt_cmd) ? I_IRQ_FETCH :

(∼cpuoff

&

~cpu halt cmd) ? I DEC

: I IDLE;

I_IRQ_FETCH: i_state_nxt = I_IRQ_DONE;

I_IRQ_DONE : i_state_nxt = I_DEC;

I DEC

: i_state_nxt = irq_detect

? I IRQ FETCH :

(cpuoff |

cpu_halt_cmd) & exec_done ? I_IDLE

cpu_halt_cmd &

(e_state==E_IDLE) ? I_IDLE

1

pc_sw_wr

? I DEC

1

```

```

~exec_done &

~(e state==E IDLE) ? I DEC

10

// Wait in decode state

(inst_sz_nxt!

=2'b00)

? I EXT1

: I DEC;

// until execution is completed

I EXT1 : i_state_nxt = pc_sw_wr

? I DEC

10

(inst sz!

=2'b01)

? I_EXT2

: I_DEC;

I EXT2

: i state nxt = I DEC;

// pragma coverage off

default

: i state nxt = I IRQ FETCH;

// pragma coverage on

endcase

```

While the actual encoding is abstracted from this code block (it is fully encoded, not one-hot), the existence of the 'default' case clearly defines what is supposed to happen when the state is not valid. If it were one-hot encoded, this line would immediately jump to I\_IRQ\_FETCH state if it ended up on a too hot two-hot situation.

It is also quickly apparent that this always@ block is not directly clocked. The sensitivity list contains 9 different signals which we might assume are synchronously clocked, and this block would be triggered whenever one or more of the signals changes. This is significant because if any one signal can be asynchronously toggled, the entire state machine will increment forward one step perhaps out of sync with the backend and rest of the architecture.

Following back the cpu\_halt\_cmd, we find:

```

// CPU on/off through the debug

interface or cpu_en port

wire cpu_halt_cmd = dbg_halt_cmd |

~cpu_en_s;

```

This is a pretty common practice. Several signals might be combined with logic into a more descriptive wire name. The disadvantage of this is that it can hide from simple inspection external factors that might allow control of a signal. For example, if there were a secure lock/unlock signal that was combined with a user-controllable input, a coder might not use the correct signal and accidentally give a usercontrollable signal influence over what should be a secured resource.

As we continue to step backwards we find:

```

always @(posedge dbg_clk or posedge dbg_rst)

if (dbg_rst) halt_flag <= 1'b0;

else if (halt_flag_clr) halt_flag <= 1'b0;

else if (halt_flag_set) halt_flag <= 1'b1;

wire dbg_halt_cmd = (halt_flag |

halt_flag_set) & ~inc_step[1];</pre>

```

dbg\_halt\_cmd depends on halt\_flag, which normally is synchronous to dbg\_clk, but the preceding always@ block is also sensitive to dbg\_rst. We have found an external signal that can be used to trigger the frontend state machine logic asynchronously.

Looking back at the state machine, we can pick out the state that might be vulnerable to this, particularly IRQ\_FETCH, IRQ\_DONE, and DEC. When timed carefully, we should be able to skip any one of these states. This means we could theoretically bypass the execution of a single instruction since we failed to fetch it, and we would likely instead execute stale data, most likely re-executing the previous instruction.

The takeaway here is to be mindful and deliberate about state transitions:

- Is your state machine strictly clocked?

- Are your sensitivity list parameters all synchronous?

- Are your critical signals 'pure' or are the combined logically with other, perhaps asynchronous or user-controlled signals?

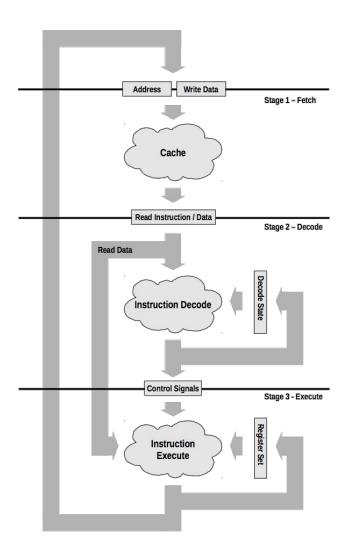

#### Amber

Amber is an open-source ARMv2 compatible core. By implementing an older version of the ARM instruction set, the project avoids patent issues with later instruction sets, however ARMv2 is not supported by recent Linux kernels.

Amber sits in between openMSP430 and OpenRISC in complexity and capacity. While it's a much more complicated and more capable architecture than MSP430, it is architected with all memory access routed over the Wishbone interface versus a native memory interfaces in ORPSoC implementations.

#### Memory, Addressing, and Caching

Our analysis of Amber focused on memory, addressing, and caching - an area that often seems simple at first glance, but is filled with nuances, conditions, exceptions, and corner cases that can be difficult to hit but have a big impact when they are. After our analysis, we actually didn't encounter any security issues that seemed potentially vulnerable. As a result, let's highlight some of the things that were done right and how they might have gone wrong.

First, let's examine the memory map, as defined in system/memory\_configuration.v:

| <pre>// e.g. 24 for 32MBytes, 26 for localparam MAIN_MSB</pre>     | <i>128MBytes</i> = 26; |

|--------------------------------------------------------------------|------------------------|

| // e.g. 13 for 4k words<br>localparam BOOT_MSB                     | = 13;                  |

| localparam MAIN_BASE<br><mark>32'h0000_0000; /* Main Memory</mark> | = */                   |

| localparam BOOT_BASE                         | =              |  |  |

|----------------------------------------------|----------------|--|--|

| 32'h0000_0000; /* Cachable Boo               | ot Memory */   |  |  |

| localparam AMBER TM BASE                     | = 16'h1300;    |  |  |

| /* Timers Module */                          |                |  |  |

| localparam AMBER IC BASE                     | = 16'h1400;    |  |  |

| /* Interrupt Controller */                   |                |  |  |

| localparam AMBER UARTO BASE                  | = 16'h1600;    |  |  |

| /* UART 0 */                                 |                |  |  |

| localparam AMBER_UART1_BASE                  | = 16'h1700:    |  |  |

| /* UART 1 */                                 | 20             |  |  |

| localparam ETHMAC BASE                       | = 16'h2000;    |  |  |

| /* Ethernet MAC */                           |                |  |  |

| localparam HIBOOT BASE                       | =              |  |  |

| 32'h2800_0000; /* Uncachable E               | Root Memory */ |  |  |

| localparam TEST BASE                         | = 16'hf000;    |  |  |

| /* Test Module */                            | - 10 111000,   |  |  |

| , reseriodate ,                              |                |  |  |

|                                              |                |  |  |

| // UART 0 address space                      |                |  |  |

|                                              |                |  |  |

| <pre>function in_uart0;</pre>                |                |  |  |

| <pre>input [31:0] address;</pre>             |                |  |  |

| begin                                        |                |  |  |

| in_uart0 = address [ <mark>31:16</mark> ] == |                |  |  |

| AMBER_UART0_BASE;                            |                |  |  |

| end                                          |                |  |  |

| endfunction                                  |                |  |  |

Here, we see the wishbone addresses where each peripheral as well as memory are mapped, followed by an example of one of the "in\_xxx" functions that returns true when a given address maps to that target peripheral. There are two common pitfalls that often happen right here.

First, overlapping memory spaces can introduce a number of problems. This is remediated by giving each device a full 64k of address space. As the code is formatted, it's plain to see the order in memory and the high 16 bits of each address range. Also thanks to the well-formated Verilog, it is quick to confirm that all of the "in\_xxx" functions properly compare the same high 16 bits against the tested address.

Second, introducing configurable memory mapping adds orders of magnitude of complexity right here. Considering this is a soft core design intended for customization on an FPGA, there are nuances to customizing this memory map that are not immediately apparent. Placing I/O devices as low as 0x13000000 limits the system to just over 128MB of memory. As memory capacity has increased, most FPGA development boards come equipped with more memory. It is not clear from this code that adjusting MAIN\_MSB beyond it's current value might be catastrophic. Do determine if, in fact, there are any memory aliasing issues, we have to examine the logic that actually resolves addresses using these functions and defines. For that we examine system/wishbone arbiter.v:

| // Arbitrate betwe                          | een sla | aves            |  |  |

|---------------------------------------------|---------|-----------------|--|--|

| <b>assign</b> current_sla                   | ave = i | in_ethmac       |  |  |

| ( master_adr ) ? 4                          | 1'd0 :  | // Ethmac       |  |  |

|                                             | i       | n_boot_mem      |  |  |

| ( master_adr ) ? 4                          | ↓'d1 :  | // Boot memory  |  |  |

|                                             | i       | ln_main_mem     |  |  |

| ( master_adr ) ? 4                          | 1'd2 :  | // Main memory  |  |  |

|                                             | i       | ln_uart0        |  |  |

| ( master_adr ) ? 4                          | 1'd3 :  | // UART 0       |  |  |

|                                             | i       | ln_uart1        |  |  |

| ( master_adr ) ? 4                          | 1'd4 :  | // UART 1       |  |  |

|                                             | i       | ln_test         |  |  |

| ( master_adr ) ? 4                          | 4'd5 :  | // Test Module  |  |  |

|                                             | i       | in_tm           |  |  |

| ( master_adr ) ? 4                          | 1'd6 :  | // Timer Module |  |  |

|                                             | i       | ln_ic           |  |  |

| ( master_adr ) ? 4                          | 1'd7 :  | // Interrupt    |  |  |

| Controller                                  |         |                 |  |  |

|                                             |         |                 |  |  |

| <pre>4'd2 ; // default to main memory</pre> |         |                 |  |  |

It is immediately clear that address resolution priority is well defined. In the event there were overlapping memory regions, the way this assignment is structured ensures that the same device would get priority over an address every time. Just as in software - the fewer different implementations of the same logic the better.

In the event the memory size were increased to 512MB, main memory would overtake the UARTs, Test module, Timer module, and interrupt controller. However, writes to 0x20000000 to 0x2000FFFF would still be directed to the Ethernet Controller creating a hole in main memory.

We can also see that any address not otherwise defined is mapped to main memory. This begs the question: What would happen if we accessed address 0x18000000? No I/O device is mapped in this region, so the access would be directed to main memory. in system/main\_mem.v:

```

//

//

// Write for 32-bit wishbone

//

always @( posedge i_clk )

begin

```

```

wr en

<= start_write;

wr mask

<= ~ i wb sel;

wr_data

<= i_wb_dat;

// Wrap the address

at 32 MB, or full width

addr dl

<= i mem ctrl ? {5'd0,

i_wb_adr[24:2]} : i_wb_adr[29:2];

if (wren)

ram [addr d1[27:2]] <=

masked wdata;

end

....

11

// Read for 32-bit wishbone

11

_____

. . . . . . . . .

assign rd_data = ram [addr_d1[27:2]];

```

Note that this is not fully a fair assessment. main\_mem.v is non synthesizable and for simulation only. However, it is a good indication of what is likely to be the behaviour of a reals system. High order bits of the address are ignored - memory simply wraps around past 128MB. This means that a write to 0x10000001 is identical to a write to 0x01. In a more complex system, it also means that a access to 0x10000001 might be able to circumvent any checks that would apply to an access to 0x01.

Since this is a very simple core with no MMU, there's no paging or memory virtualization to bypass here. Also, ARMv2's privilege levels don't confer any different access to memory, so there's no additional exploit here that wouldn't have been possible via a more direct approach.

Despite the fact that no further vulnerability was discovered, the pathways left open on this system are indicative of what could be found in more complicated systems, and could be used to bypass security measures. When evaluating memory, addressing, and caching, consider:

- What devices live in the memory map?

- How are they allocated? Ordered? Prioritized?

- If there are multiple implementations of address decoding, do they decode overlaps with the same priority?

- Do memory aliases exist? Can they be used to bypass protections?

#### Summary

In the course of reviewing multiple different opensource Verilog projects, a number of potential vulnerabilities were identified. The vulnerabilities highlighted are representative of security related issues commonly seen in hardware designs. To recap:

- Different state encoding schemes have different benefits. If possible, validate current states, and define the behavior for when an invalid state occurs. Depending on design, this could be done with separate combinational logic or could be as easy as more carefully defining default cases of case statements.

- Examine interesting pathways through state machines. The most direct route makes the most sense, but if alternate routes exist they should be validated.

- Every signal in a sensitivity list is granted a small degree of influence over a block of logic. Be sure that the correct signals are in the list, and if possible isolate separate blocks of logic to separate sensitivity lists with only the relevant signals.

- Combining signals may help code readability but also opens the door for unexpected inputs into a block of logic. Trace critical signals backwards to make sure their cone of logic does not include attackercontrollable signals.

- It is critical to iron out the details of a system's memory map. Mirroring, overlapping, and decode priority can all cause trouble, especially in systems that depend on decoding for access control.

## Conclusion

Exploitable hardware security bugs do exist in production systems. There is very little black art

involved in finding these bugs when the source code is available. Basic hardware security validation is well within the capabilities of most silicon developers and validators, so long as they take the time to understand the importance of a product's security requirements.

#### References

- Fuzzing the RTL: <u>http://conference.hitb.org/hitbsecconf20</u> <u>10kul/materials/D1T2%20-%20Mary</u> <u>%20Yeoh%20-%20Fuzzing%20the</u> <u>%20RTL.pdf</u>

- HSDL: A Security Development Lifecycle for hardware technologies: <u>http://ieeexplore.ieee.org/xpl/abstractAut</u> <u>hors.jsp?arnumber=6224330</u>

- A Survey of Frequently Identified Vulnerabilities in Commercial Computing Semiconductors: <u>http://ieeexplore.ieee.org/xpl/articleDetai</u> <u>ls.jsp?arnumber=5955008&navigation=1</u>

- Threat analysis for hardware and software products using HazOP: <u>http://dl.acm.org/citation.cfm?</u> <u>id=1569853</u>

- Practical Secure Hardware Design for Embedded Systems: <u>http://www.grandideastudio.com/wp-</u> <u>content/uploads/secure\_embed\_paper.p</u> <u>df</u>

- An efficient algorithm for identifying security relevant logic and vulnerabilities in RTL designs: <u>http://ieeexplore.ieee.org/xpl/login.jsp?</u>

<u>tp=&arnumber=6581567</u>